Product Summary

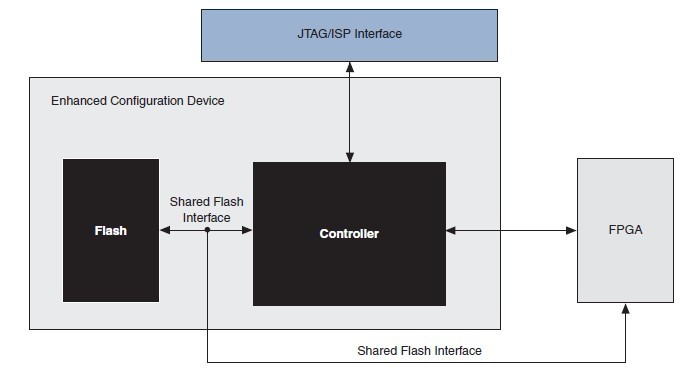

The Altera enhanced configuration device EP2C8F256C8N is a single-device, high-speed, advanced configuration solution for very high-density FPGAs. The core of the enhanced configuration device EP2C8F256C8N is divided into two major blocks: a configuration controller and a flash memory. The flash memory of EP2C8F256C8N is used to store configuration data for systems made up of one or more Altera FPGAs. Unused portions of the flash memory can be used to store processor code or data that can be accessed via the external flash interface after FPGA configuration is complete.

Parametrics

EP2C8F256C8N absolute maximum ratings: (1)VCC Supply voltage With respect to ground: -0.2 to 4.6 V; (2)VI DC input voltage With respect to ground: -0.5 to 3.6 V; (3)IMAX DC VCC or ground current: 100 mA; (4)IOUT DC output current, per pin: -25 to 25 mA; (5)PD Power dissipation: 360 mW; (6)TSTG Storage temperature: No bias -65 to 150 ℃; (7)TAMB Ambient temperature Under bias: -65 to 135 ℃; (8)TJ Junction temperature Under bias: 135 ℃.

Features

EP2C8F256C8N features: (1)Single-chip configuration solution for Altera ACEX 1K, APEX 20K (including APEX 20K, APEX 20KC, and APEX 20KE), APEX II, Arria GX, Cyclone, Cyclone II, FLEX 10K (including FLEX 10KE and FLEX 10KA), Mercury, Stratix II, and Stratix II GX devices; (2)Contains 4-, 8-, and 16-Mbit flash memories for configuration data storage; (3)On-chip decompression feature almost doubles the effective configuration density; (4)Standard flash die and a controller die combined into single stacked chip package; (5)Supports byte-wide configuration mode fast passive parallel (FPP); 8-bit data output per DCLK cycle; (6)Supports true n-bit concurrent configuration (n = 1, 2, 4, and 8) of Altera FPGAs; (7)Pin-selectable 2-ms or 100-ms power-on reset (POR) time; (8)Available in the 100-pin plastic quad flat pack (PQFP) and the 88-pin Ultra FineLine BGAR (UFBGA) packages; (9)Vertical migration between all devices supported in the 100-pin PQFP package; (10)Supply voltage of 3.3 V (core and I/O); (11)Hardware compliant with IEEE Std. 1532 in-system programmability (ISP) specification; (12)Supports ISP via Jam Standard Test and Programming Language (STAPL); (13)Supports JTAG boundary scan; (14)nINIT_CONF pin allows private JTAG instruction to start FPGA configuration; (15)Internal pull-up resistor on nINIT_CONF always enabled; (16)User programmable weak internal pull-up resistors on nCS and OE pins; (17)Internal weak pull-up resistors on external flash interface address and control lines, bus hold on data lines; (18)Standby mode with reduced power consumption.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

EP2C8F256C8N |

|

IC CYCLONE II FPGA 8K 256-FBGA |

Data Sheet |

|

|

||||||

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|

EP2C15AF256C6N |

|

IC CYCLONE II FPGA 15K 256-FBGA |

Data Sheet |

|

|

||||||

|

EP2C15AF256C7N |

|

IC CYCLONE II FPGA 15K 256-FBGA |

Data Sheet |

|

|

||||||

|

EP2C15AF256C8N |

|

IC CYCLONE II FPGA 15K 256-FBGA |

Data Sheet |

|

|

||||||

|

EP2C15AF256I8N |

|

IC CYCLONE II FPGA 15K 256-FBGA |

Data Sheet |

|

|

||||||

|

EP2C15AF484C6N |

|

IC CYCLONE II FPGA 15K 484-FBGA |

Data Sheet |

|

|

||||||

|

EP2C15AF484C7N |

|

IC CYCLONE II FPGA 15K 484-FBGA |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))