Product Summary

The K4J52324QE-BJ1A is 536,870,912 bits of hyper synchronous data rate Dynamic RAM organized as 8 x 2,097,152 words by 32 bits, fabricated with SAMSUNG high performance CMOS technology. Synchronous features with Data Strobe allow extremely high performance up to 8GB/s/chip. I/O transactions are possible on both edges of the clock cycle. Range of operating frequencies, and programmable latencies allow the K4J52324QE-BJ1A to be useful for a variety of high performance memory system applications.

Parametrics

K4J52324QE-BJ1A absolute maixmum ratings: (1)Voltage on any pin relative to Vss VIN, VOUT: -0.5 ~ VDDQ + 0.5V; (2)Voltage on VDD supply relative to Vss VDD: -0.5 ~ 2.5 V; (3)Voltage on VDDQ supply relative to Vss VDDQ: -0.5 ~ 2.5 V; (4)MAX Junction Temperature TJ: +125 ℃; (5)Storage temperature TSTG: -55 ~ +150 ℃; (6)Power dissipation PD: 4 W; (7)Short Circuit Output Current IOS: 50 mA.

Features

K4J52324QE-BJ1A features: (1)On-Die Termination (ODT); (2)Output Driver Strength adjustment by EMRS; (3)Calibrated output drive; (4)1.8V Pseudo Open drain compatible inputs/outputs; (5)8 internal banks for concurrent operation; (6)Differential clock inputs (CK and CK); (7)Commands entered on each positive CK edge; (8)CAS latency : 7, 8, 9, 10, 11, 12,13 (clock); (9)Programmable Burst length : 4 and 8; (10)Programmable Write latency : 1, 2, 3, 4, 5, 6 and 7 (clock); (11)Single ended READ strobe (RDQS) per byte; (12)Single ended WRITE strobe (WDQS) per byte; (13)RDQS edge-aligned with data for READs; (14)WDQS center-aligned with data for WRITEs; (15)Data Mask(DM) for masking WRITE data; (16)Auto & Self refresh modes; (17)Auto Precharge option; (18)32ms, auto refresh (8K cycle); (19)136 Ball FBGA; (20)Maximum clock frequency up to 1000MHz; (21)Maximum data rate up to 2.0Gbps/pin; (22)DLL for outputs; (23)Boundary scan function with SEN pin; (24)Mirror function with MF pin.

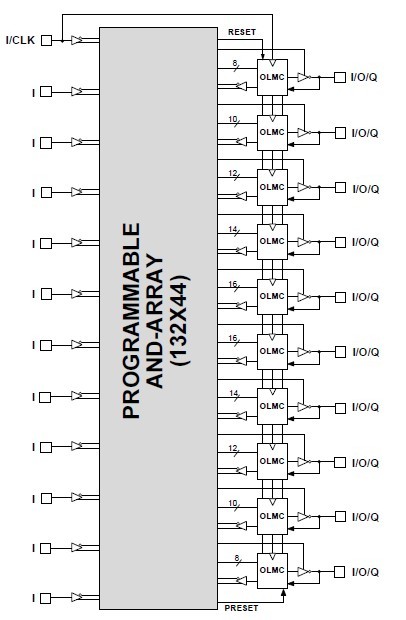

Diagrams

|

K4J52324QC-B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K4J55323QF-GC |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))